What is continuity, why it is needed?

There are 3 types of continuity: N-well, P-well & power continuity without continuity, the design rules dictate that you will need to space things further apart. Also, the wells need to be tied to a single global VDD/VSS so as to tap power only at one point anywhere in the standard cell row. Thus, all the wells & power lines of individual standard cells have to be tied to maintain continuity.

N-well continuity:

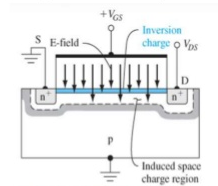

It is a fabrication issue. Creation of mask is costly. If you have single N-well mask, you can easily fabricate. If you separate N-well masks, there is chances of Well Proximity Effects (WPE) which may vary electrical parameters of your device.

N-well continuity:

It is a fabrication issue. Creation of mask is costly. If you have single N-well mask, you can easily fabricate. If you separate N-well masks, there is chances of Well Proximity Effects (WPE) which may vary electrical parameters of your device.

1. What is the need for filler cells??

In standard cells APR flow, the cells in the design are placed on the row. To make sure that each cells gets power and ground connection, the cells are abutted together son that the VDD and VSS terminal of neighboring cells short together. This makes it possible to tap power only at one point anywhere in the row. But it is virtually impossible to fill 100% of the die area with regular cells. So we use filler cells to fill there spaces between regular library cells to route power rails.

In standard cells APR flow, the cells in the design are placed on the row. To make sure that each cells gets power and ground connection, the cells are abutted together son that the VDD and VSS terminal of neighboring cells short together. This makes it possible to tap power only at one point anywhere in the row. But it is virtually impossible to fill 100% of the die area with regular cells. So we use filler cells to fill there spaces between regular library cells to route power rails.

- Filler cells are used for connecting the gaps between the cells after placement.

In short, Filler cells primarily are non-functional cells used to continue the VDD and VSS rails (i.e. when performing automatic PnR using standard cells there will be discontinuity in power, ground and diffusion layers because all the cells will not be abutting.).

They serve 2 main purposes:

- They reduce the DRC violations created by the base (N-well, P-plus & N-plus) layers.

- They help maintain the power rail connection continuity.

3. When are they inserted into the PD flow?

- After Routing and Timing closure, but before LVS and DRC.

- Filling 100% of the area with regular cells is generally impossible. We need spaces to improve the placement and routing. Once we complete the routing and achieve the timing closure, we may need to fill the empty spaces with filler cells.

- They a re inserted into the flow after your timing, placement opt and DRC cleanup. They are inserted to meet your utilization targets so as to avoid sagging of layers after fab and to ensure n-well continuity. Once the placement is done (after meeting the timing in PnR) you need to run command to add filler cells and tool will automatically add filler cells where ever there is empty space between standard cells.

- As you ask the SoC - ENCOUNTER tool to place the filler cells, it fills the gaps in the design in standard cell rows with different variety of filler cells as per the gaps availability, however there will be overlaps, you can delete the overlapping ones.

Basically filler cells will make power/ground and n-well continuity. There will be power/ground open between the standard cells (empty space) and also may be n-well spacing DRC error.

5. What are the other uses of Filler cells?

- Filler cells don't have functionality. They have power rails, N-well, P-plus, N-plus layer only. If we want to do any Engineering Change Order (ECO's) then the filler cells can be deleted and the empty spaces can be utilized. They can also be used to cope with setup or hold violations.

- Some filler cells have caps in them for decoupling capacitor. But De-cap cells are quite different from the filler cells, while there can as Decoupling capacitance's. Decap cells can help to reduce IR drop or reduce noise in mixed signal designs.

- I don't really think that filler cells can solve any metal density issues. It is usually solved by metal fill option in the tool. Metal density rule arises out of another fab constraints, to physically support the substrate minimum metal density that should be maintained throughout the die area on all the layer.

- Filler cells don't play any role in Latch-up prevention. For Latch-up prevention, we use TAP cells.