The MOS

transistor, also called MOSFET (Metal-Oxide-Semiconductor Field-Effect

Transistor) or IGFET (Insulated-Gate

Field-Effect Transistor)

is the most widely used semiconductor device and is at the heart of every

digital circuit. Without the MOSFET there would be no computer industry, no

digital telecommunication systems, no video games, no pocket calculators and no

digital wristwatches. MOS transistors are also increasingly used in analog

applications such as switched capacitor circuits, analog-to-digital converters,

and filters.

The

exponential progress of MOS technology is best illustrated by the evolution of

the number of MOS transistors integrated in a single memory chip or single

microprocessor, as a function of calendar year. Each memory cell of a dynamic

random-access memory (DRAM) contains a MOS transistor and a capacitor. This

exponential growth of integration density with time is known as Moore's law.

The

integration density of memory circuits is about 5 to 10 times higher than that

of logic circuits such as microprocessors because of the more repetitive layout

of transistors in memory chips. The increase in integration density is

essentially due to the reduction of transistor size.

There are two

types of MOS transistors: n-channel MOSFET, p- channel MOSFET.

N-channel MOSFET: The n-channel MOSFET in which current flow is due to electron transport, and the p-channel MOSFET in which holes are responsible for current flow. A circuit containing only n-channel devices is produced by an nMOS process.

N-channel MOSFET: The n-channel MOSFET in which current flow is due to electron transport, and the p-channel MOSFET in which holes are responsible for current flow. A circuit containing only n-channel devices is produced by an nMOS process.

P-channel MOSFET:

In a p-channel transistor an N-type substrate is used. The P-type drain is at a lower potential than the P-type source and the application of a negative bias to the gate enables the formation of a hole-enriched channel between source and drain. The metal-insulator semiconductor structure is often referred to as a "MIS" structure, where the "I" stands for the insulator. When the insulator is an oxide, it is called a "MOS" structure.

In a p-channel transistor an N-type substrate is used. The P-type drain is at a lower potential than the P-type source and the application of a negative bias to the gate enables the formation of a hole-enriched channel between source and drain. The metal-insulator semiconductor structure is often referred to as a "MIS" structure, where the "I" stands for the insulator. When the insulator is an oxide, it is called a "MOS" structure.

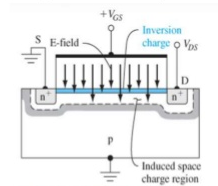

OPERATION OF N-CHANNEL MOSFET:

The basic

operation of the n-channel MOSFET is the following. We will first consider the

case where the gate voltage is equal to zero while the P type substrate and the

source are grounded The drain is connected to a positive voltage source for

instance). Since the source and the substrate are at the same potential there

is no current flow in the source-substrate junction. The drain-substrate

junction is reverse biased and except for a small negligible reverse leakage

current no current flows in that junction either. Under these conditions there

is no channel formation, and therefore, no current flow from source to drain. In

the second case a constant positive bias is applied to the gate. There is no

gate current since the metal electrode is dielectrically insulated from the

silicon. Because it is positively biased the gate electrode does, however,

attract electrons from the semiconductor, and a thin, electron rich layer forms

under the gate insulator. These electrons are supplied by the source and the

drain which, being N-type, are large reservoirs of electrons. The electron-rich

layer underneath the gate is called "channel". The N-type source and

the N-type drain are connected by the electron rich channel, and current is now

free to flow between source and drain. The effect of the gate voltage

controlling the concentration of electrons in the semiconductor through the

gate oxide is called "field effect". The bias on the gate creates an

electric field which can either induce or inhibit the formation of an

electron-rich region at the surface of the semiconductor. The terms

"source", "drain", "channel" and "gate"

come to mind quite naturally since the electrons originate at the source, flow through

the channel and are finally collected by the drain, the whole process being

controlled by the bias on the gate.

The basic

operation of the n-channel MOSFET is the following. We will first consider the

case where the gate voltage is equal to zero while the P type substrate and the

source are grounded The drain is connected to a positive voltage source for

instance). Since the source and the substrate are at the same potential there

is no current flow in the source-substrate junction. The drain-substrate

junction is reverse biased and except for a small negligible reverse leakage

current no current flows in that junction either. Under these conditions there

is no channel formation, and therefore, no current flow from source to drain. In

the second case a constant positive bias is applied to the gate. There is no

gate current since the metal electrode is dielectrically insulated from the

silicon. Because it is positively biased the gate electrode does, however,

attract electrons from the semiconductor, and a thin, electron rich layer forms

under the gate insulator. These electrons are supplied by the source and the

drain which, being N-type, are large reservoirs of electrons. The electron-rich

layer underneath the gate is called "channel". The N-type source and

the N-type drain are connected by the electron rich channel, and current is now

free to flow between source and drain. The effect of the gate voltage

controlling the concentration of electrons in the semiconductor through the

gate oxide is called "field effect". The bias on the gate creates an

electric field which can either induce or inhibit the formation of an

electron-rich region at the surface of the semiconductor. The terms

"source", "drain", "channel" and "gate"

come to mind quite naturally since the electrons originate at the source, flow through

the channel and are finally collected by the drain, the whole process being

controlled by the bias on the gate.

In the above equations "lamda" is Channel length modulation.

|

Body effect is major drawback of CMOS technology. This will effect when substrate or body not biased with source. There is PN-juction diode present in between substrate and source so this will effect the change of threshold voltage. in order to avoid this effect we have to give same potential to both substrate and source.

In Body effect when we give the supply voltage to the gate (+ ve) and source to (- ve) at this condition there will be formation of a diode in the reverse bias this will increase the depletion region this makes the decreasing the channel and the threshold voltage will also increases, so in order to maintain the channel we need to increase the gate voltage.

Due to this effect we are biasing the source and substrate to the same potential which will not allow the moment of depletion towards the gate by this the Threshold voltage will not be increased.

Channel Length Modulation :

To understand the Channel length modulation, first we need to know about pinch-off of the channel is introduced. The channel is formed by attraction of carriers to the gate and the current drawn through the channel is nearly a constant independent of drain voltage in saturation mode.

As the drain voltage increases, its control over the current extends further towards source, so the uninverted region expands towards the source, shortening the length of the channel region. The effect is called Channel Length Modulation. Because resistance is proportional to length, shortening the channel decreases its resistance, causing an increase in current with increase in drain bias for a MOSFET operating in saturation region.